# COMPUTER ORGANIZATION & ASSEMBLY LANGUAGE

www.eiilmuniversity.ac.in

#### **SYLLABUS**

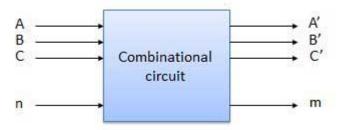

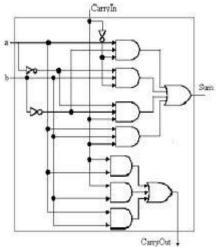

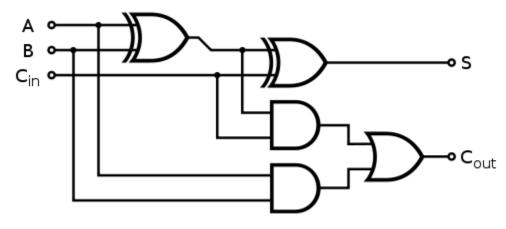

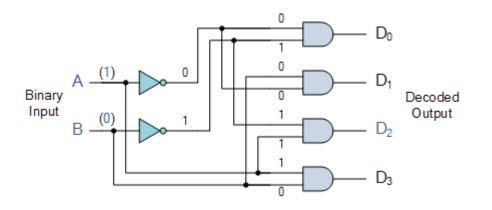

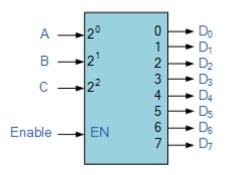

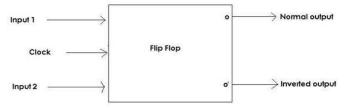

#### The Computer and its Components

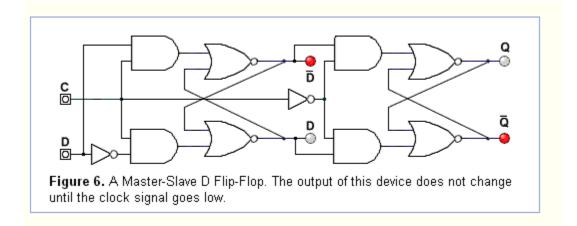

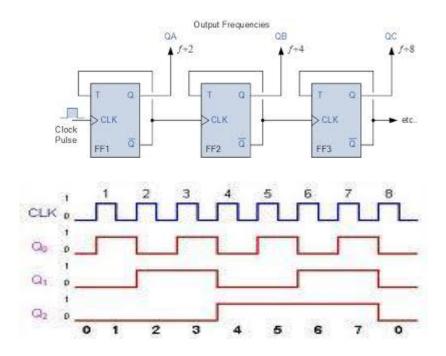

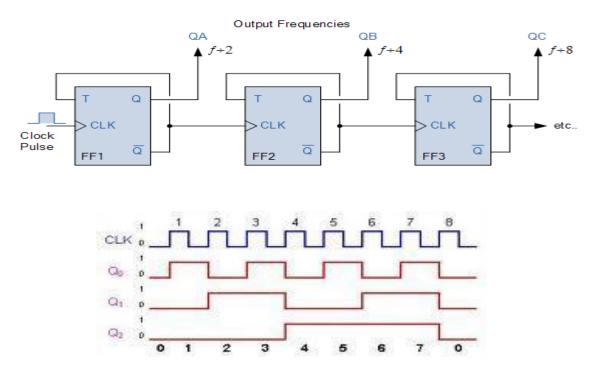

History of Computing, Data representation, Number System, Fixed Point Number Representation, Floating Point Number Representation, BCD representation, Error Detection Code, Fixed and Instruction execution, Interrupts, Buses, Boolean Algebra, Logic Circuits, Logic Gates, Combinational circuits, Sequential Circuit, Adders, Decoders, Multiplexer, Encoder, Types Of Flip Flop, Edge Triggered, Master-Slave, Asynchronous (Serial Or Ripple) Counters, Shift Register

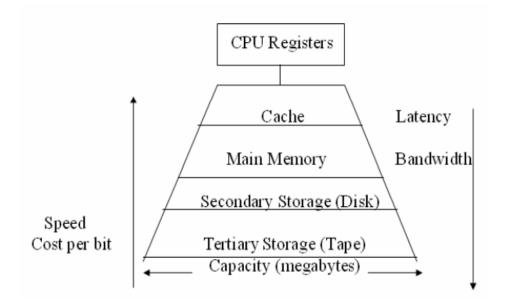

#### Memory System

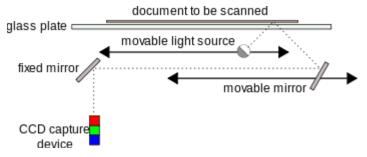

Memory Hierarchy, RAM, DRAM, SRAM, ROM, Flash Memory, Secondary memory, Optical Memories, Hard disk drives, Head Mechanisms, CCDs, Bubble memories, RAID, Cache Organisation, Memory System of Micro-Computers, Input/ Output System, DMA, Input output processors, External Communication Interfaces, Interrupt Processing, BUS arbitration, Floppy Drives, CD-ROM, DVD-ROM, Cartridge Drives, Recordable CDs, CD-RW, Input/ Output Technologies, Characteristics, Video Cards, Monitors, USB Port, Liquid Crystal Display (LCD), Sound Cards, Modems, Printers, Scanner, Digital Cameras, Keyboard, Mouse, Power supply.

#### **Central Processing Unit**

The Instruction and instruction Set, Addressing modes and their importance, Register, Micro-operation, Description of Various types of Registers with the help of a Microprocessor example, ALU, Control Unit, Hardwired Control, Wilkes control, Micro-programmed control, Microinstructions,

#### **Assembly Language Programming**

Microprocessor, Instruction format for an example Microprocessor, The need and use of assembly language, Input output in assembly Language Program, Assembly Programming tools, Interfacing assembly with HLL, Device Deriver of assembly language, Interrupts in assembly language programming,

Suggested Reading:

• Verma, G.; Mielke, N. *Reliability performance of ETOX based flash memories*. IEEE International Reliability Physics Symposium.

- Doron D. Swade . Redeeming Charles Babbage's Mechanical Computer. Scientific American

- Meuer, Hans; Strohmaier, Erich; Simon, Horst; Dongarra, Jack . "Architectures Share Over Time". TOP500.

- Lavington, Simon . A History of Manchester Computers (2 ed.). Swindon: The British Computer Society

- Stokes, Jon . *Inside the Machine: An Illustrated Introduction to Microprocessors and Computer Architecture*. San Francisco: No Starch Press.

- Zuse, Konrad . The Computer My life. Berlin: Pringler-Verlag.

# **Computer Organization & Assembly Language**

# 1.1 The computer and its components

A **computer** is a general purpose device that can be programmed to carry out a set of arithmetic or logical operations. Since a sequence of operations can be readily changed, the computer can solve more than one kind of problem.

Conventionally, a computer consists of at least one processing element, typically a central processing unit (CPU) and some form of memory. The processing element carries out arithmetic and logic operations, and a sequencing and control unit that can change the order of operations based on stored information. Peripheral devices allow information to be retrieved from an external source, and the result of operations saved and retrieved.

The first electronic digital computers were developed between 1940 and 1945. Originally they were the size of a large room, consuming as much power as several hundred modern personal computers (PCs). In this era mechanical analog computers were used for military applications.

Modern computers based on integrated circuits are millions to billions of times more capable than the early machines, and occupy a fraction of the space. Simple computers are small enough to fit into mobile devices, and mobile computers can be powered by small batteries. Personal computers in their various forms are icons of the Information Age and are what most people think of as "computers." However, the embedded computers found in many devices from MP3 players to fighter aircraft and from toys to industrial robots are the most numerous.

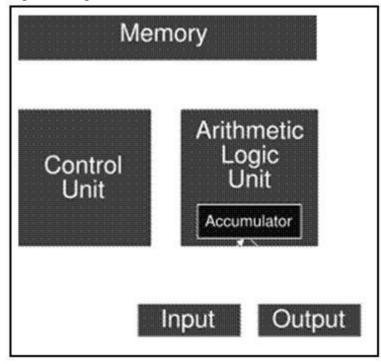

# 1.1.1 Components

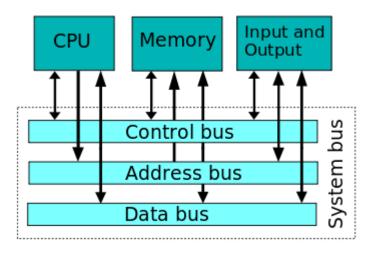

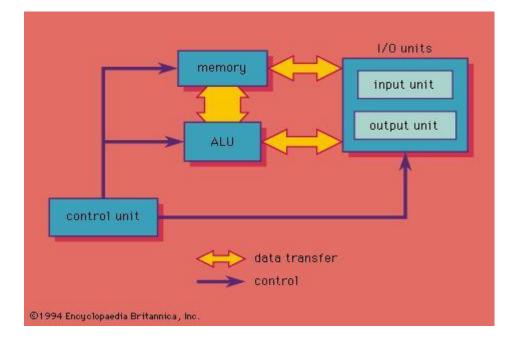

A general purpose computer has four main components: the arithmetic logic unit (ALU), the control unit, the memory, and the input and output devices (collectively termed I/O). These parts are interconnected by buses, often made of groups of wires.

Inside each of these parts are thousands to trillions of small electrical circuits which can be turned off or on by means of an electronic switch. Each circuit represents a bit (binary digit) of information so that when the circuit is on it represents a "1", and when off it represents a "0" (in positive logic representation). The circuits are arranged in logic gates so that one or more of the circuits may control the state of one or more of the other circuits.

The control unit, ALU, registers, and basic I/O (and often other hardware closely linked with these) are collectively known as a central processing unit (CPU). Early CPUs were composed of many separate components but since the mid-1970s CPUs have typically been constructed on a single integrated circuit called a microprocessor.

#### **Control unit**

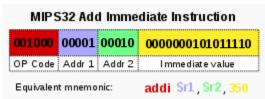

Diagram showing how a particular MIPS architecture instruction would be decoded by the control system.

The control unit (often called a control system or central controller) manages the computer's various components; it reads and interprets (decodes) the program instructions, transforming them into a series of control signals which activate other parts of the computer Control systems in advanced computers may change the order of some instructions so as to improve performance.

A key component common to all CPUs is the program counter, a special memory cell (a register) that keeps track of which location in memory the next instruction is to be read from.

The control system's function is as follows—note that this is a simplified description, and some of these steps may be performed concurrently or in a different order depending on the type of CPU:

- 1. Read the code for the next instruction from the cell indicated by the program counter.

- 2. Decode the numerical code for the instruction into a set of commands or signals for each of the other systems.

- 3. Increment the program counter so it points to the next instruction.

- 4. Read whatever data the instruction requires from cells in memory (or perhaps from an input device). The location of this required data is typically stored within the instruction code.

- 5. Provide the necessary data to an ALU or register.

- 6. If the instruction requires an ALU or specialized hardware to complete, instruct the hardware to perform the requested operation.

- 7. Write the result from the ALU back to a memory location or to a register or perhaps an output device.

- 8. Jump back to step (1).

Since the program counter is (conceptually) just another set of memory cells, it can be changed by calculations done in the ALU. Adding 100 to the program counter would cause the next instruction to be read from a place 100 locations further down the program. Instructions that modify the program counter are often known as "jumps" and allow for loops (instructions that are repeated by the computer) and often conditional instruction execution (both examples of control flow). The sequence of operations that the control unit goes through to process an instruction is in itself like a short computer program, and indeed, in some more complex CPU designs, there is another yet smaller computer called a microsequencer, which runs a microcode program that causes all of these events to happen.

# 1.1.1.1 Arithmetic logic unit (ALU)

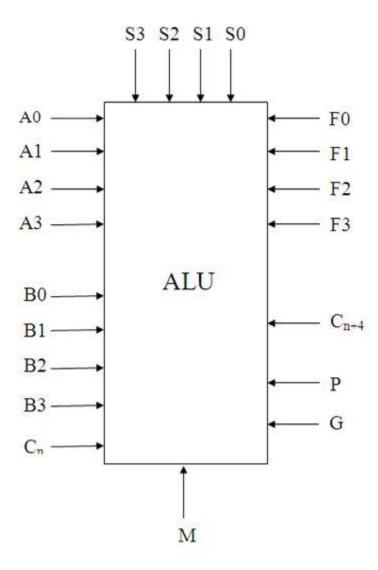

The ALU is capable of performing two classes of operations: arithmetic and logic.

The set of arithmetic operations that a particular ALU supports may be limited to addition and subtraction, or might include multiplication, division, trigonometry functions such as sine, cosine, etc., and square roots. Some can only operate on whole numbers (integers) whilst others use floating point to represent real numbers, albeit with limited precision. However, any computer that is capable of performing just the simplest operations can be programmed to break down the more complex operations into simple steps that it can perform. Therefore, any computer can be programmed to perform any arithmetic operation—although it will take more time to do so if its ALU does not directly support the operation. An ALU may also compare numbers and returnboolean truth values (true or false) depending on whether one is equal to, greater than or less than the other ("is 64 greater than 65?").

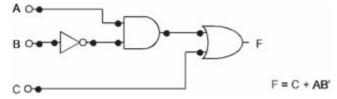

Logic operations involve Boolean logic: AND, OR, XOR and NOT. These can be useful for creating complicated conditional statements and processing boolean logic.

Superscalar computers may contain multiple ALUs, allowing them to process several instructions simultaneously. Graphics processors and computers with SIMD and MIMD features often contain ALUs that can perform arithmetic on vectors and matrices.

# 1.1.1.2 Memory

A computer's memory can be viewed as a list of cells into which numbers can be placed or read. Each cell has a numbered "address" and can store a single number. The computer can be instructed to "put the number 123 into the cell numbered 1357" or to "add the number that is in cell 1357 to the number that is in cell 2468 and put the answer into cell 1595." The information stored in memory may represent practically anything. Letters, numbers, even computer instructions can be placed into memory with equal ease. Since the CPU does not differentiate between different types of information, it is the software's responsibility to give significance to what the memory sees as nothing but a series of numbers.

In almost all modern computers, each memory cell is set up to store binary numbers in groups of eight bits (called a byte). Each byte is able to represent 256 different numbers ( $2^8 = 256$ ); either from 0 to 255 or -128 to +127. To store larger numbers, several consecutive bytes may be used (typically, two, four or eight). When negative numbers are required, they are usually stored in two's complement notation. Other arrangements are possible, but are usually not seen outside of specialized applications or historical contexts. A computer can store any kind of information in memory if it can be represented numerically. Modern computers have billions or even trillions of bytes of memory.

The CPU contains a special set of memory cells called registers that can be read and written to much more rapidly than the main memory area. There are typically between two and one hundred registers depending on the type of CPU. Registers are used for the most frequently needed data items to avoid having to access main memory every time data is needed. As data is constantly being worked on, reducing the need to access main memory (which is often slow compared to the ALU and control units) greatly increases the computer's speed.

Computer main memory comes in two principal varieties: random-access memory or RAM and read-only memory or ROM. RAM can be read and written to anytime the CPU commands it, but ROM is preloaded with data and software that never changes, therefore the CPU can only read from it. ROM is typically used to store the computer's initial start-up instructions. In general, the contents of RAM are erased when the power to the computer is turned off, but ROM retains its data indefinitely. In a PC, the ROM contains a specialized program called the BIOS that orchestrates loading the computer's operating system from the hard disk drive into RAM whenever the computer is turned on or reset. In embedded computers, which frequently do not have disk drives, all of the required software may be stored in ROM. Software stored in ROM is often called firmware, because it is notionally more like hardware than software. Flash memory blurs the distinction between ROM and RAM, as it retains its data when turned off but is also rewritable. It is typically much slower than conventional ROM and RAM however, so its use is restricted to applications where high speed is unnecessary.

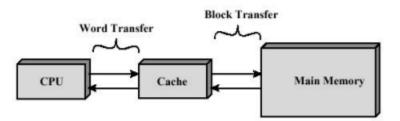

In more sophisticated computers there may be one or more RAM cache memories, which are slower than registers but faster than main memory. Generally computers with this sort of cache are designed to move frequently needed data into the cache automatically, often without the need for any intervention on the programmer's part.

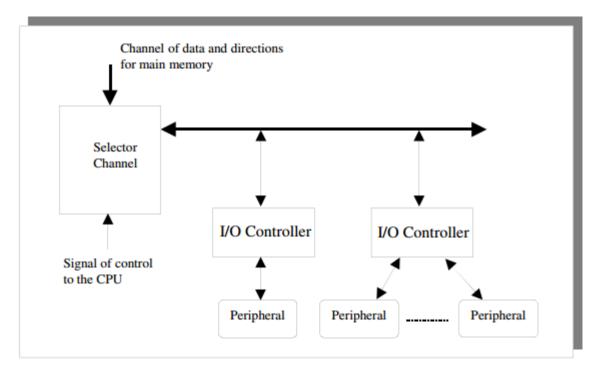

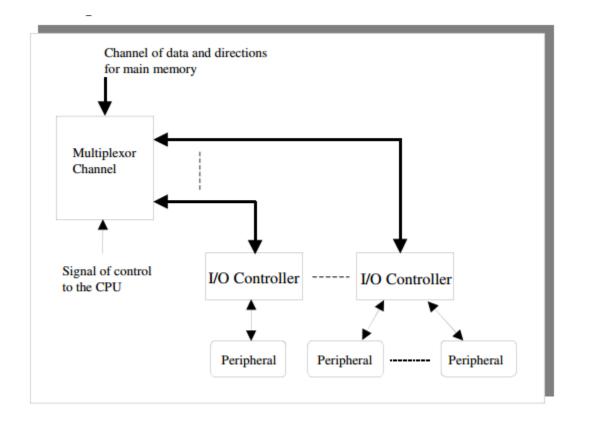

# 1.1.1.3 Input/output (I/O)

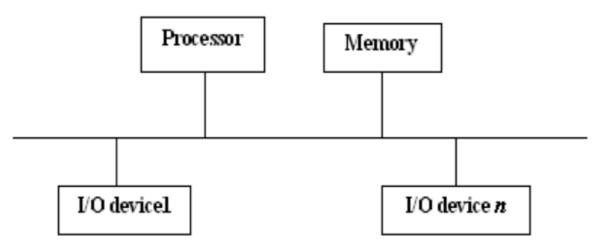

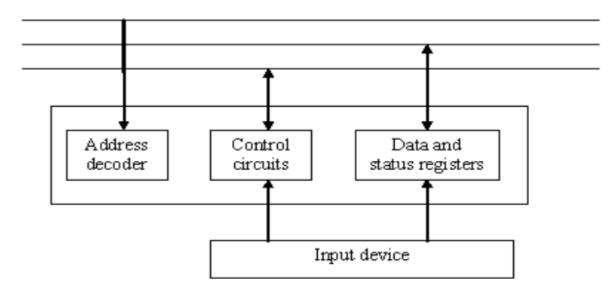

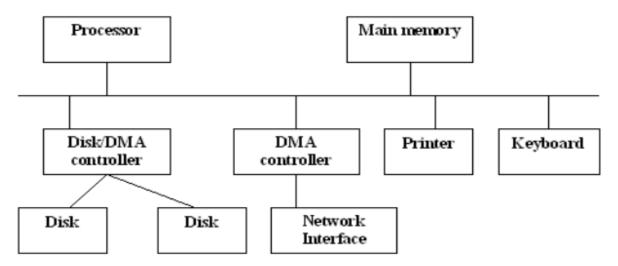

I/O is the means by which a computer exchanges information with the outside world. Devices that provide input or output to the computer are calledperipherals. On a typical personal computer, peripherals include input devices like the keyboard and mouse, and output devices such as the displayand printer. Hard disk drives, floppy disk drives and optical disc drives serve as both input and output devices. Computer networking is another form of I/O.

I/O devices are often complex computers in their own right, with their own CPU and memory. A graphics processing unit might contain fifty or more tiny computers that perform the calculations necessary to display 3D graphics.<sup>[citation needed]</sup> Modern desktop computers contain many smaller computers that assist the main CPU in performing I/O.

# 1.1.1.4 Multitasking

While a computer may be viewed as running one gigantic program stored in its main memory, in some systems it is necessary to give the appearance of running several programs simultaneously. This is achieved by multitasking i.e. having the computer switch rapidly between running each program in turn. One means by which this is done is with a special signal called an interrupt, which can periodically cause the computer to stop executing instructions where it was and do something else instead. By remembering where it was executing prior to the interrupt, the

computer can return to that task later. If several programs are running "at the same time," then the interrupt generator might be causing several hundred interrupts per second, causing a program switch each time. Since modern computers typically execute instructions several orders of magnitude faster than human perception, it may appear that many programs are running at the same time even though only one is ever executing in any given instant. This method of multitasking is sometimes termed "time-sharing" since each program is allocated a "slice" of time in turn

Before the era of cheap computers, the principal use for multitasking was to allow many people to share the same computer.

Seemingly, multitasking would cause a computer that is switching between several programs to run more slowly, in direct proportion to the number of programs it is running, but most programs spend much of their time waiting for slow input/output devices to complete their tasks. If a program is waiting for the user to click on the mouse or press a key on the keyboard, then it will not take a "time slice" until the event it is waiting for has occurred. This frees up time for other programs to execute so that many programs may be run simultaneously without unacceptable speed loss.

# 1.1.1.5 Multiprocessing

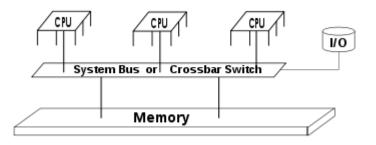

Some computers are designed to distribute their work across several CPUs in a multiprocessing configuration, a technique once employed only in large and powerful machines such as supercomputers, mainframe computers and servers. Multiprocessor and multi-core (multiple CPUs on a single integrated circuit) personal and laptop computers are now widely available, and are being increasingly used in lower-end markets as a result.

Supercomputers in particular often have highly unique architectures that differ significantly from the basic stored-program architecture and from general purpose computers.<sup>[53]</sup> They often feature thousands of CPUs, customized high-speed interconnects, and specialized computing hardware. Such designs tend to be useful only for specialized tasks due to the large scale of program organization required to successfully utilize most of the available resources at once. Supercomputers usually see usage in large-scale simulation, graphics rendering, and cryptography applications, as well as with other so-called "embarrassingly parallel" tasks.

# **1.1.1.6 Networking and the Internet**

Computers have been used to coordinate information between multiple locations since the 1950s. The U.S. military's SAGE system was the first large-scale example of such a system, which led to a number of special-purpose commercial systems such asSabre.

In the 1970s, computer engineers at research institutions throughout the United States began to link their computers together using telecommunications technology. The effort was funded by ARPA (now DARPA), and the computer network that resulted was called the ARPANET. The technologies that made the Arpanet possible spread and evolved.

In time, the network spread beyond academic and military institutions and became known as the Internet. The emergence of networking involved a redefinition of the nature and boundaries of

the computer. Computer operating systems and applications were modified to include the ability to define and access the resources of other computers on the network, such as peripheral devices, stored information, and the like, as extensions of the resources of an individual computer. Initially these facilities were available primarily to people working in high-tech environments, but in the 1990s the spread of applications like e-mail and the World Wide Web, combined with the development of cheap, fast networking technologies like Ethernet andADSL saw computer networking become almost ubiquitous. In fact, the number of computers that are networked is growing phenomenally. A very large proportion of personal computers regularly connect to the Internet to communicate and receive information. "Wireless" networking, often utilizing mobile phone networks, has meant networking is becoming increasingly ubiquitous even in mobile computing environments.

# **1.2 History of Computing**

The first use of the word "computer" was recorded in 1613 in a book called "The yong mans gleanings" by English writer Richard Braithwait I haue read the truest computer of Times, and the best Arithmetician that euer breathed, and he reduceth thy dayes into a short number. It referred to a person who carried out calculations, or computations, and the word continued with the same meaning until the middle of the 20th century. From the end of the 19th century the word began to take on its more familiar meaning, a machine that carries out computations.

# 1.2.1 Limited-function early computers

The history of the modern computer begins with two separate technologies, automated calculation and programmability. However no single device can be identified as the earliest computer, partly because of the inconsistent application of that term. A few devices are worth mentioning though, like some mechanical aids to computing, which were very successful and survived for centuries until the advent of the electronic calculator, like the Sumerian abacus, designed around 2500 BC of which a descendant won a speed competition against a contemporary desk calculating machine in Japan in 1946 theslide rules, invented in the 1620s, which were carried on five Apollo space missions, including to the moon and arguably the astrolabe and theAntikythera mechanism, an ancient astronomical analog computer built by the Greeks around 80 BC The Greek mathematician Hero of Alexandria (c. 10–70 AD) built a mechanical theater which performed a play lasting 10 minutes and was operated by a complex system of ropes and drums that might be considered to be a means of deciding which parts of the mechanism performed which actions and when. This is the essence of programmability.

Blaise Pascal invented the mechanical calculator in 1642, known as Pascal's calculator, it was the first machine to better human performance of arithmetical computations and would turn out to be the only functional mechanical calculator in the 17th century. Two hundred years later, in 1851,Thomas de Colmar released, after thirty years of development, his simplified arithmometer; it became the first machine to be commercialized because it was strong enough and reliable enough to be used daily in an office environment. The mechanical calculator was at the root of the development of computers in two separate ways. Initially, it was in trying to develop more powerful and more flexible calculators<sup>[12]</sup> that the computer was first theorized by Charles Babbage and then developed. Secondly, development of a low-cost electronic calculator,

successor to the mechanical calculator, resulted in the development by Intel of the first commercially availablemicroprocessor integrated circuit.

# **1.2.2 First general-purpose computers**

In 1801, Joseph Marie Jacquard made an improvement to the textile loom by introducing a series of punched paper cards as a template which allowed his loom to weave intricate patterns automatically. The resulting Jacquard loom was an important step in the development of computers because the use of punched cards to define woven patterns can be viewed as an early, albeit limited, form of programmability.

It was the fusion of automatic calculation with programmability that produced the first recognizable computers. In 1837, Charles Babbage was the first to conceptualize and design a fully programmablemechanical computer, his analytical engine. Limited finances and Babbage's inability to resist tinkering with the design meant that the device was never completed— nevertheless his son, Henry Babbage, completed a simplified version of the analytical engine's computing unit (the mill) in 1888. He gave a successful demonstration of its use in computing tables in 1906. This machine was given to the Science museum in South Kensington in 1910.

Between 1842 and 1843, Ada Lovelace, an analyst of Charles Babbage's analytical engine, translated an article by Italian military engineer Luigi Menabrea on the engine, which she supplemented with an elaborate set of notes of her own, simply called Notes. These notes contain what is considered the first computer program – that is, an algorithm encoded for processing by a machine. Lovelace's notes are important in the early history of computers. She also developed a vision on the capability of computers to go beyond mere calculating or number-crunching while others, including Babbage himself, focused only on those capabilities.

In the late 1880s, Herman Hollerith invented the recording of data on a machine-readable medium. Earlier uses of machine-readable media had been for control, not data. "After some initial trials with paper tape, he settled on punched cards... To process these punched cards he invented the tabulator, and the keypunch machines. These three inventions were the foundation of the modern information processing industry. Large-scale automated data processing of punched cards was performed for the 1890 United States Census by Hollerith's company, which later became the core of IBM. By the end of the 19th century a number of ideas and technologies, that would later prove useful in the realization of practical computers, had begun to appear:Boolean algebra, the vacuum tube (thermionic valve), punched cards and tape, and the teleprinter.

During the first half of the 20th century, many scientific computing needs were met by increasingly sophisticated analog computers, which used a direct mechanical or electrical model of the problem as a basis for computation. However, these were not programmable and generally lacked the versatility and accuracy of modern digital computers.

Alan Turing is widely regarded as the father of modern computer science. In 1936, Turing provided an influential formalization of the concept of the algorithmand computation with the Turing machine, providing a blueprint for the electronic digital computer.<sup>[23]</sup> Of his role in the creation of the modern computer, Time magazine in naming Turing one of the 100 most influential people of the 20th century, states: "The fact remains that everyone who taps at a

keyboard, opening a spreadsheet or a word-processing program, is working on an incarnation of a Turing machine.

The first really functional computer was the Z1, originally created by Germany's Konrad Zuse in his parents living room in 1936 to 1938, and it is considered to be the first electro-mechanical binary programmable (modern) computer.

George Stibitz is internationally recognized as a father of the modern digital computer. While working at Bell Labs in November 1937, Stibitz invented and built a relay-based calculator he dubbed the "Model K" (for "kitchen table," on which he had assembled it), which was the first to usebinary circuits to perform an arithmetic operation. Later models added greater sophistication including complex arithmetic and programmability.

The Atanasoff–Berry Computer (ABC) was the world's first electronic digital computer, albeit not programmable. Atanasoff is considered to be one of the fathers of the computer. Conceived in 1937 by Iowa State College physics professor John Atanasoff, and built with the assistance of graduate student Clifford Berry,<sup>[28]</sup> the machine was not programmable, being designed only to solve systems of linear equations. The computer did employ parallel computation. A 1973 court ruling in a patent dispute found that the patent for the 1946 ENIAC computer derived from the Atanasoff–Berry Computer.

The first program-controlled computer was invented by Konrad Zuse, who built the Z3, an electromechanical computing machine, in 1941. The first programmable electronic computer was the Colossus, built in 1943 by Tommy Flowers.

# 1.2.3 Key steps towards modern computers

A succession of steadily more powerful and flexible computing devices were constructed in the 1930s and 1940s, gradually adding the key features that are seen in modern computers. The use of digital electronics (largely invented by Claude Shannon in 1937) and more flexible programmability were vitally important steps, but defining one point along this road as "the first digital electronic computer" is difficult.

Notable achievements include:

- Konrad Zuse's electromechanical "Z machines." The Z3 (1941) was the first working machine featuring binary arithmetic, including floating point arithmetic and a measure of programmability. In 1998 the Z3 was proved to be Turing complete, therefore being the world's first operational computer. Thus, Zuse is often regarded as the inventor of the computer.

- The non-programmable Atanasoff–Berry Computer (commenced in 1937, completed in 1941) which used vacuum tube based computation, binary numbers, and regenerative capacitor memory. The use of regenerative memory allowed it to be much more compact than its peers (being approximately the size of a large desk or workbench), since intermediate results could be stored and then fed back into the same set of computation elements.

- The secret British Colossus computers (1943), which had limited programmability but demonstrated that a device using thousands of tubes could be reasonably reliable and electronically re-programmable. It was used for breaking German wartime codes.

- The Harvard Mark I (1944), a large-scale electromechanical computer with limited programmability.

- The U.S. Army's Ballistic Research Laboratory ENIAC (1946), which used decimal arithmetic and is sometimes called the first general purposeelectronic computer (since Konrad Zuse's Z3 of 1941 used electromagnets instead of electronics). Initially, however, ENIAC had an architecture which required rewiring a plugboard to change its programming.

# **1.2.4 Stored-program architecture**

Several developers of ENIAC, recognizing its flaws, came up with a far more flexible and elegant design, which came to be known as the "stored-program architecture" or von Neumann architecture. This design was first formally described by John von Neumann in the paper First Draft of a Report on the EDVAC, distributed in 1945. A number of projects to develop computers based on the stored-program architecture commenced around this time, the first of which was completed in 1948 at the University of Manchester in England, the Manchester Small-Scale Experimental Machine (SSEM or "Baby"). The Electronic Delay Storage Automatic Calculator (EDSAC), completed a year after the SSEM at Cambridge University, was the first practical, non-experimental implementation of the stored-program design and was put to use immediately for research work at the university. Shortly thereafter, the machine originally described by von Neumann's paper—EDVAC—was completed but did not see full-time use for an additional two years.

Nearly all modern computers implement some form of the stored-program architecture, making it the single trait by which the word "computer" is now defined. While the technologies used in computers have changed dramatically since the first electronic, general-purpose computers of the 1940s, most still use the von Neumann architecture.

Beginning in the 1950s, Soviet scientists Sergei Sobolev and Nikolay Brusentsov conducted research on ternary computers, devices that operated on a base three numbering system of -1, 0, and 1 rather than the conventional binary numbering system upon which most computers are based. They designed the Setun, a functional ternary computer, at Moscow State University. The device was put into limited production in the Soviet Union, but supplanted by the more common binary architecture.

# **1.2.5 Semiconductors and microprocessors**

Computers using vacuum tubes as their electronic elements were in use throughout the 1950s, but by the 1960s they had been largely replaced bytransistor-based machines, which were smaller, faster, cheaper to produce, required less power, and were more reliable. The first transistorized computer was demonstrated at the University of Manchester in 1953. In the 1970s, integrated circuit technology and the subsequent creation ofmicroprocessors, such as the Intel 4004, further decreased size and cost and further increased speed and reliability of computers. By the late 1970s, many products such as video recorders contained dedicated

computers called microcontrollers, and they started to appear as a replacement to mechanical controls in domestic appliances such as washing machines. The 1980s witnessed home computers and the now ubiquitous personal computer. With the evolution of the Internet, personal computers are becoming as common as the television and the telephone in the household Modern smartphones are fully programmable computers in their own right, and as of 2009 may well be the most common form of such computers in existence.<sup>1</sup>

#### Programs

The defining feature of modern computers which distinguishes them from all other machines is that they can be programmed. That is to say that some type of instructions (the program) can be given to the computer, and it will process them. Modern computers based on the von Neumann architectureoften have machine code in the form of an imperative programming language.In practical terms, a computer program may be just a few instructions or extend to many millions of instructions, as do the programs for word processors and web browsers for example. A typical modern computer can execute billions of instructions per second (gigaflops) and rarely makes a mistake over many years of operation. Large computer programs consisting of several million instructions may take teams of programmers years to write, and due to the complexity of the task almost certainly contain errors.

#### Stored program architecture

This section applies to most common RAM machine-based computers.

In most cases, computer instructions are simple: add one number to another, move some data from one location to another, send a message to some external device, etc. These instructions are read from the computer's memory and are generally carried out (executed) in the order they were given. However, there are usually specialized instructions to tell the computer to jump ahead or backwards to some other place in the program and to carry on executing from there. These are called "jump" instructions (or branches). Furthermore, jump instructions may be made to happen conditionally so that different sequences of instructions may be used depending on the result of some previous calculation or some external event. Many computers directly support subroutines by providing a type of jump that "remembers" the location it jumped from and another instruction to return to the instruction following that jump instruction.

Program execution might be likened to reading a book. While a person will normally read each word and line in sequence, they may at times jump back to an earlier place in the text or skip sections that are not of interest. Similarly, a computer may sometimes go back and repeat the instructions in some section of the program over and over again until some internal condition is met. This is called the flow of control within the program and it is what allows the computer to perform tasks repeatedly without human intervention.

Comparatively, a person using a pocket calculator can perform a basic arithmetic operation such as adding two numbers with just a few button presses. But to add together all of the numbers from 1 to 1,000 would take thousands of button presses and a lot of time, with a near certainty of making a mistake. On the other hand, a computer may be programmed to do this with just a few simple instructions. For example:

mov No. 0, sum ; set sum to 0

mov No. 1, num ; set num to 1

loop: add num, sum ; add num to sum

add No. 1, num ; add 1 to num

cmp num, #1000 ; compare num to 1000

ble loop ; if num <= 1000, go back to 'loop'

halt ; end of program. stop running</pre>

Once told to run this program, the computer will perform the repetitive addition task without further human intervention. It will almost never make a mistake and a modern PC can complete the task in about a millionth of a second

## Bugs

Errors in computer programs are called "bugs." They may be benign and not affect the usefulness of the program, or have only subtle effects. But in some cases, they may cause the program or the entire system to "hang," becoming unresponsive to input such as mouse clicks or keystrokes, to completely fail, or to crash. Otherwise benign bugs may sometimes be harnessed for malicious intent by an unscrupulous user writing an exploit, code designed to take advantage of a bug and disrupt a computer's proper execution. Bugs are usually not the fault of the computer. Since computers merely execute the instructions they are given, bugs are nearly always the result of programmer error or an oversight made in the program's design.

Admiral Grace Hopper, an American computer scientist and developer of the first compiler, is credited for having first used the term "bugs" in computing after a dead moth was found shorting a relay in the Harvard Mark II computer in September 1947.

#### Machine code

In most computers, individual instructions are stored as machine code with each instruction being given a unique number (its operation code or opcodefor short). The command to add two numbers together would have one opcode, the command to multiply them would have a different opcode and so on. The simplest computers are able to perform any of a handful of different instructions; the more complex computers have several hundred to choose from, each with a unique numerical code. Since the computer's memory is able to store numbers, it can also store the instruction codes. This leads to the important fact that entire programs (which are just lists of these instructions) can be represented as lists of numbers and can themselves be manipulated inside the computer in the same way as numeric data. The fundamental concept of storing programs in the computer's memory alongside the data they operate on is the crux of the von Neumann, or stored program, architecture. In some cases, a computer might store some or all of its program in memory that is kept separate from the data it operates on. This is called the Harvard architecture after the Harvard Mark I computer. Modern von Neumann computers display some traits of the Harvard architecture in their designs, such as in CPU caches.

While it is possible to write computer programs as long lists of numbers (machine language) and while this technique was used with many early computers, it is extremely tedious and potentially error-prone to do so in practice, especially for complicated programs. Instead, each basic instruction can be given a short name that is indicative of its function and easy to remember – a mnemonic such as ADD, SUB, MULT or JUMP. These mnemonics are collectively known as a computer's assembly language. Converting programs written in assembly language into something the computer can actually understand (machine language) is usually done by a computer program called an assembler.

#### **Programming language**

Programming languages provide various ways of specifying programs for computers to run. Unlike natural languages, programming languages are designed to permit no ambiguity and to be concise. They are purely written languages and are often difficult to read aloud. They are generally either translated into machine code by a compiler or an assembler before being run, or translated directly at run time by an interpreter. Sometimes programs are executed by a hybrid method of the two techniques.

#### Low-level languages

Machine languages and the assembly languages that represent them (collectively termed lowlevel programming languages) tend to be unique to a particular type of computer. For instance, an ARM architecture computer (such as may be found in a PDA or a hand-held videogame) cannot understand the machine language of an Intel Pentium or the AMD Athlon 64 computer that might be in a PC.

#### **Higher-level languages**

Though considerably easier than in machine language, writing long programs in assembly language is often difficult and is also error prone. Therefore, most practical programs are written in more abstract high-level programming languages that are able to express the needs of the programmer more conveniently (and thereby help reduce programmer error). High level languages are usually "compiled" into machine language (or sometimes into assembly language and then into machine language) using another computer program called a compiler. High level languages are less related to the workings of the target computer than assembly language, and more related to the language and structure of the problem(s) to be solved by the final program. It is therefore often possible to use different compilers to translate the same high level language program into the machine language of many different types of computer. This is part of the means by which software like video games may be made available for different computer architectures such as personal computers and various video game consoles.

#### **Program design**

Program design of small programs is relatively simple and involves the analysis of the problem, collection of inputs, using the programming constructs within languages, devising or using established procedures and algorithms, providing data for output devices and solutions to the problem as applicable. As problems become larger and more complex, features such as subprograms, modules, formal documentation, and new paradigms such as object-oriented programming are encountered. Large programs involving thousands of line of code and more require formal software methodologies. The task of developing large software systems presents a significant intellectual challenge. Producing software with an acceptably high reliability within a predictable schedule and budget has historically been difficult; the academic and professional discipline of software engineering concentrates specifically on this challenge.

# **1.3 Data representation**

Computers can sense when an electrical signal being sent is either on or off. This is represented by a '1' (on) or a '0' (off). Each individual 1 or 0 is called a **binary digit** or **bit** and it is the smallest piece of data that a computer system can work with.

Eight bits are grouped together to make one byte.

One byte provides enough codes (256) to represent all of the characters that appear on a standard keyboard. A byte is the basic unit used to measure computer memory size.

#### A table displaying the values of computer memory

| Bit           | 1 or 0         |

|---------------|----------------|

| Byte          | 8 Bits         |

| Kilobyte (Kb) | 1024 bytes     |

| Megabyte (Mb) | 1024 kilobytes |

| Gigabyte (Gb) | 1024 megabytes |

| Terabyte (Tb) | 1024 gigabytes |

#### **Representation of positive whole numbers**

We can represent any number, however large, in binary. Remember we can only store numbers between 0 and 255 in **one byte**. This is obviously rather restrictive since it's not dealing with large integers, negative numbers or decimal numbers.

## The representation of numbers in binary

| <b>2</b> <sup>7</sup> | 2 <sup>6</sup> | <b>2</b> <sup>5</sup> | <b>2</b> <sup>4</sup> | <b>2</b> <sup>3</sup> | <b>2</b> <sup>2</sup> | <b>2</b> <sup>1</sup> | 2 <sup>0</sup> | first eight binary powers                             |

|-----------------------|----------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------|-------------------------------------------------------|

| 128                   | 64             | 32                    | 16                    | 8                     | 4                     | 2                     | 1              |                                                       |

| 0                     | 1              | 0                     | 0                     | 0                     | 0                     | 1                     | 1              | =67                                                   |

| 1                     | 1              | 1                     | 1                     | 1                     | 1                     | 1                     | 1              | =255: the largest number represented in just one byte |

| 0                     | 0              | 0                     | 0                     | 1                     | 1                     | 0                     | 0              | =12                                                   |

## Advantages of using binary numbers

- They have only two states 1 or 0 (on or off)

- Simple Arithmetic has only two states, i.e. 0+0, 0+1, 1+0, 1+1

- A drop in the voltage (degradation) will not affect the data

## **Floating Point Representation**

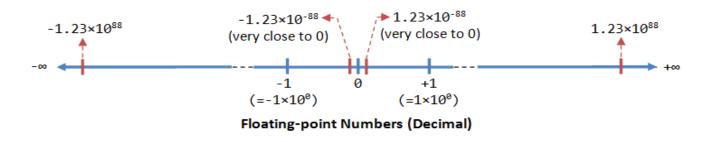

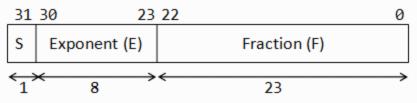

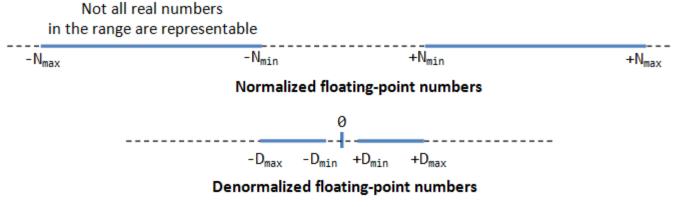

Floating Point Representation is used to approximate very large or very accurate numbers.

## In Decimal

76 = .76 x 100 = .76 x 102

- .76 mantissa

- 10 base

- 2 exponent

## In Binary

$1001100 = .1001100 \ge 27 = .1001100 \ge 2111$

- .1001100 mantissa

- 2 base

- 111 exponent

Remember Binary is base 2 as there are only two numbers 1 and 0.

## Storing text (ASCII)

Each character on the keyboard has a unique one byte (8-bits) code to represent it. A standard for representing these characters is the **ASCII set**.**ASCII** stands for the American Standard Code for Information Interchange. Characters like letters **a** to **z** and **A** to **Z**, the digits **0** to **9** and symbols \$, £, ?, @, etc, are each given a standard code which is the same on all computer systems.

A table showing different representations of a list of characters in binary, and decimal

| Character | Binary    | Decimal | Character | Binary    | Decimal |

|-----------|-----------|---------|-----------|-----------|---------|

| Space     | 0010 0000 | 32      | А         | 0100 0001 | 65      |

| !         | 0010 0001 | 33      | В         | 0100 0010 | 66      |

| ,         | 0010 0010 | 34      | С         | 0100 0011 | 67      |

| 1         | 0011 0001 | 49      | Y         | 0101 1001 | 89      |

| 2         | 0011 0010 | 50      | Z         | 0101 1010 | 90      |

| 3         | 0011 0011 | 51      | А         | 0110 0001 | 97      |

| ?         | 0011 1111 | 63      | В         | 0110 0010 | 98      |

| @         | 0100 0000 | 64      | С         | 0110 0011 | 99      |

The whole range of characters recognised by a computer system is known as the**character set** of that computer. All the keys on the keyboard, i.e. capital letters (A-Z), small letters (a-z), numbers (0-9).

#### Bit map graphic representation

Graphics on the screen are made up of tiny dots called **pixels**. The more pixels on the screen, the better (clearer) the picture or resolution. The state of each pixel is stored in memory. The colour of each dot can either be black (1) or white (0). The higher the image resolution, the more memory that is needed to store the graphic.

#### **Storage requirements**

You may need to calculate the storage required for a black and white graphic in the exam. To do this you:

- multiply the pixels across by the pixels down to get the total number of **pixels** (dots), this equals the numbers of **bits**

- divide by 8 to get the number of **bytes**

- divide by 1024 to get the number of **kilobytes**

- divide by 1024 to get the number of **megabytes**

| $\longrightarrow$                           | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

|---------------------------------------------|---|---|---|---|---|---|---|---|---|---|

| $\longrightarrow$                           | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| $\longrightarrow$                           | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| $\blacksquare\blacksquare \longrightarrow$  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| $\blacksquare \blacksquare \longrightarrow$ | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| $ \longrightarrow $                         | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| $\blacksquare \blacksquare \longrightarrow$ | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

| $\blacksquare \longrightarrow$              | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| $\blacksquare \longrightarrow$              | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| $\longrightarrow$                           | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

Using the above example we will calculate the storage requirements for the image.

10 pixels x 11 pixels = 110 pixels (= 110 bits)

110 ÷ 8 = 13.75 bytes

Using the above example we will calculate the storage requirements for the image.

500 pixels x 700 pixels = 350000 pixels (= 350000 bits)

350000 ÷ 8 = 43750 bytes

43750 ÷ **1024** = 42.72 kilobytes

#### Example

Graphic 7 inches x 5 inches with 600dpi. Calculate the amount of memory required to store the graphic.

- (7 x 600) x (5 x 600) = 4200 x 3000 **pixels**

- = 12600000 pixels (÷ 8)

- = 1575000 bytes ( $\div 1024$ )

- = 1538.08 Kb ( $\div$  1024)

- = 1.5 **Mb**

# 1.4 Number System

There are several number systems which we normally use, such as decimal, binary, octal, hexadecimal, etc. Amongst them we are most familiar with the decimal number system. These systems are classified according to the values of the base of the number system. The number system having the value of the base as 10 is called a decimal number system, whereas that with a base of 2 is called a binary number system. Likewise, the number systems having base 8 and 16 are called octal and hexadecimal number systems respectively.

With a decimal system we have 10 different digits, which are 0, 1, 2, 3, 4, 5, 6, 7, 8, and 9. But a binary system has only 2 different digits—0 and 1. Hence, a binary number cannot have

any digit other than 0 or 1. So to deal with a binary number system is quite easier than a decimal system. Now, in a digital world, we can think in binary nature, *e.g.*, a light can be either off or on. There is no state in between these two. So we generally use the binary system when we deal with the digital world. Here comes the utility of a binary system. We can express everything in the world with the help of only two digits *i.e.*, 0 and 1. For example, if we want to express  $25_{10}$  in binary we may write  $11001_2$ . The right most digit in a number system is called the 'Least Significant Bit' (LSB) or 'Least Significant Digit' (LSD). And the left most digit in a number system is called the 'Most Significant Bit' (MSB) or 'Most Significant Digit' (MSD). Now normally when we deal with different number systems we specify the base as the subscript to make it clear which number system is being used.

In an octal number system there are 8 digits—0, 1, 2, 3, 4, 5, 6, and 7. Hence, any octal number cannot have any digit greater than 7. Similarly, a hexadecimal number system has 16 digits—0 to 9— and the rest of the six digits are specified by letter symbols as A, B, C, D, E, and F. Here A, B, C, D, E, and F represent decimal 10, 11, 12, 13, 14, and 15 respectively. Octal and hexadecimal codes are useful to write assembly level language.

In general, we can express any number in any base or radix "X." Any number with base X, having *n* digits to the left and *m* digits to the right of the decimal point can be expressed as:

$$a_n X^{n-1} + a_{n-1} X^{n-2} + a_{n-2} X^{n-3} + \ldots + a_2 X^1 + a_1 X^0 + b_1 X^{-1} + b_2 X^{-2} + \ldots + b_m X^{-m}$$

where  $a_n$  is the digit in the *n*th position. The coefficient  $a_n$  is termed as the MSD or Most Significant Digit and  $b_m$  is termed as the LSD or the Least Significant Digit.

#### **1.4.1 Conversion between Number System**

It is often required to convert a number in a particular number system to any other number system, *e.g.*, it may be required to convert a decimal number to binary or octal or hexadecimal. The reverse is also true, *i.e.*, a binary number may be converted into decimal and so on. The methods of interconversions are now discussed.

#### **1.4.1.1 Decimal-to-Binary Conversion**

Now to convert a number in decimal to a number in binary we have to divide the decimal number by 2 repeatedly, until the quotient of zero is obtained. This method of repeated division by 2 is called the 'double-dabble' method. The remainders are noted down for each

of the division steps. Then the column of the remainder is read in reverse order *i.e.*, from bottom to top order. We try to show the method with an example shown in Example 1.1.

| Solution. | Division | Quotient | Generated remainder |

|-----------|----------|----------|---------------------|

|           | 26/2     | 13       | 0                   |

|           | 13/2     | 6        | 1                   |

|           | 6/2      | 3        | 0                   |

|           | 3/2      | 1        | 1                   |

|           | 1/2      | 0        | 1                   |

**Example 1.1.** Convert 26<sub>10</sub> into a binary number.

Hence the converted binary number is  $11010_2$ .

#### 1.4.1.2 Decimal-to-Octal Conversion

Similarly, to convert a number in decimal to a number in octal we have to divide the decimal number by 8 repeatedly, until the quotient of zero is obtained. This method of repeated division by 8 is called 'octal-dabble.' The remainders are noted down for each of the division steps. Then the column of the remainder is read from bottom to top order, just as in the case of the double-dabble method. We try to illustrate the method with an example shown in Example 1.2.

Example 1.2. Convert 426<sub>10</sub> into an octal number.

| Solution. | Division | Quotient | Generated remainder |

|-----------|----------|----------|---------------------|

|           | 426/8    | 53       | 2                   |

|           | 53/8     | 6        | 5                   |

|           | 6/8      | 0        | 6                   |

|           |          |          |                     |

Hence the converted octal number is  $652_8$ .

#### 1.4.1.3 Decimal-to-Hexadecimal Conversion

The same steps are repeated to convert a number in decimal to a number in hexadecimal. Only here we have to divide the decimal number by 16 repeatedly, until the quotient of zero is obtained. This method of repeated division by 16 is called 'hex-dabble.' The remainders are noted down for each of the division steps. Then the column of the remainder is read from bottom to top order as in the two previous cases. We try to discuss the method with an example shown in Example 1.3.

**Example 1.3.** Convert 348<sub>10</sub> into a hexadecimal number.

| Solution. | Division | Quotient | Generated remainder |

|-----------|----------|----------|---------------------|

|           | 348/16   | 21       | 12                  |

|           | 21/16    | 1        | 5                   |

|           | 1/16     | 0        | 1                   |

Hence the converted hexadecimal number is  $15C_{16}$ .

#### 1.2.1.4 Binary-to-Decimal Conversion

Now we discuss the reverse method, *i.e.*, the method of conversion of binary, octal, or hexadecimal numbers to decimal numbers. Now we have to keep in mind that each of the binary, octal, or hexadecimal number system is a positional number system, *i.e.*, each of the digits in the number systems discussed above has a positional weight as in the case of the decimal system. We illustrate the process with the help of examples.

**Example 1.4.** *Convert* 10110<sub>2</sub> *into a decimal number.*

| <b>Solution.</b> The binary number given is | 10110 |

|---------------------------------------------|-------|

| Positional weights                          | 43210 |

The positional weights for each of the digits are written in italics below each digit. Hence the decimal equivalent number is given as:

$$1*2^{4} + 0*2^{3} + 1*2^{2} + 1*2^{1} + 0*2^{0}$$

= 16 + 0 + 4 + 2 + 0

= 22<sub>10</sub>

Hence we find that here, for the sake of conversion, we have to multiply each bit with its positional weights depending on the base of the number system.

#### 1.4.1.5 Octal-to-Decimal Conversion

**Example 1.5.** Convert 3462<sub>8</sub> into a decimal number.

Solution. The octal number given is3 4 6 2Positional weights3 2 1 0

The positional weights for each of the digits are written in italics below each digit. Hence the decimal equivalent number is given as:

$$= 3*8^3 + 4*8^2 + 6*8^1 + 2*8^0$$

= 1536 + 256 + 48 + 2 $= 1842_{10}$

#### 1.4.1.6 Hexadecimal-to-Decimal Conversion

**Example 1.6.** Convert 42AD<sub>16</sub> into a decimal number.

Solution. The hexadecimal number given is4 2 A DPositional weights3 2 1 0

The positional weights for each of the digits are written in italics below each digit. Hence the decimal equivalent number is given as:

$$= 4*16^{3} + 2*16^{2} + 10*16^{1} + 13*16^{0}$$

= 16384 + 512 + 160 + 13

= 17069<sub>10</sub>

#### 1.4.1.7 Fractional Conversion

So far we have dealt with the conversion of integer numbers only. Now if the number contains the fractional part we have to deal in a different way when converting the number from a different number system (*i.e.*, binary, octal, or hexadecimal) to a decimal number system or vice versa. We illustrate this with examples.

Example 1.7. Convert  $1010.011_2$  into a decimal number.Solution. The binary number given is $1 \ 0 \ 1 \ 0. \ 0 \ 1 \ 1$

Positional weights 3 2 1 0 -1-2-3

The positional weights for each of the digits are written in italics below each digit. Hence the decimal equivalent number is given as:

$= 1*2^{3} + 0*2^{2} + 1*2^{1} + 0*2^{0} + 0*2^{-1} + 1*2^{-2} + 1*2^{-3}$ = 8 + 0 + 2 + 0 + 0 + .25 + .125 = 10.375<sub>10</sub>

**Example 1.8.** Convert 362.35<sub>8</sub> into a decimal number.

Solution. The octal number given is3 6 2. 3 5Positional weights2 1 0 -1-2The positional weights for each of the digits are written in italics below each digit. Hence the decimal equivalent number is given as:

$$= 3*8^{2} + 6*8^{1} + 2*8^{0} + 3*8^{-1} + 5*8^{-2}$$

= 192 + 48 + 2 + .37 + .078125

#### $= 242.452125_{10}$

Example 1.9. Convert 42A.1216 into a decimal number.

Solution. The hexadecimal number given is4 2 A. 1 2Positional weights2 1 0 -1-2

The positional weights for each of the digits are written in italics below each digit. Hence the decimal equivalent number is given as:

$$= 4*16^{2} + 2*16^{1} + 10*16^{0} + 1*16^{-1} + 2*16^{-2}$$

= 1024 + 32 + 10 + .0625 + .00393625

= 1066.066406215\_{10}

**Example 1.10.** Convert 25.625<sub>10</sub> into a binary number.

| Solution. | Division | Quotient | Generated remainder |

|-----------|----------|----------|---------------------|

|           | 25/2     | 12       | 1                   |

|           | 12/2     | 6        | 0                   |

|           | 6/2      | 3        | 0                   |

|           | 3/2      | 1        | 1                   |

|           | 1/2      | 0        | 1                   |

|           |          |          |                     |

Therefore,  $(25)_{10} = (11001)_2$

**Fractional Part**

| .625 * 2 = 1.250 | 1 |

|------------------|---|

| .250 * 2 = .500  | 0 |

| .500 * 2 = 1.000 | 1 |

*i.e.*,  $(0.625)_{10} = (0.101)_2$

Therefore,  $(25.625)_{10} = (11001.101)_2$

**Example 1.11.** Convert 34.525<sub>10</sub> into an octal number.

| Solution.  | Division             | Quotient | Generated remainder |

|------------|----------------------|----------|---------------------|

|            | 34/8                 | 4        | 2                   |

|            | 4/8                  | 0        | 4                   |

| Therefore, | $(34)_{10} = (42)_8$ |          |                     |

|            |                      |          |                     |

**Fractional Part**

| .525 * 8 = 4.200 | 4 |

|------------------|---|

| .200 * 8 = 1.600 | 1 |

.600 \* 8 = 4.800 4 *i.e.*,  $(0.525)_{10} = (0.414)_8$

Therefore,  $(34.525)_{10} = (42.411)_8$

**Example 1.12.** Convert 92.85<sub>10</sub> into a hexadecimal number.

| Solution.                          | Division                   | Quotient           | Generated remainder |

|------------------------------------|----------------------------|--------------------|---------------------|

|                                    | 92/16                      | 5                  | 12                  |

|                                    | 5/16                       | 0                  | 5                   |

| Therefore, (                       | $(92)_{10} = (5C)_{16}$    |                    |                     |

|                                    |                            |                    |                     |

| Fractional P                       | art                        |                    |                     |

|                                    | .85                        | * 16 = 13.60       | 13                  |

|                                    | .60                        | * 16 = 9.60        | 9                   |

| <i>i.e.</i> , (0.85) <sub>10</sub> | $=(0.D9)_{16}$             |                    |                     |

| Therefore, (                       | $(92.85)_{10} = (5C)_{10}$ | .D9) <sub>16</sub> |                     |

#### 1.4.1.8 Conversion from a Binary to Octal Number and Vice Versa

We know that the maximum digit in an octal number system is 7, which can be represented as  $111_2$  in a binary system. Hence, starting from the LSB, we group three digits at a time and replace them by the decimal equivalent of those groups and we get the final octal number.

**Example 1.13.** Convert 101101010<sub>2</sub> into an equivalent octal number.

| Solution. The binary number given is  | 101 | 1010 | )10 |

|---------------------------------------|-----|------|-----|

| Starting with LSB and grouping 3 bits | 101 | 101  | 010 |

| Octal equivalent                      | 5   | 5    | 2   |

Hence the octal equivalent number is  $(552)_8$ .

**Example 1.14.** Convert 1011110<sub>2</sub> into an equivalent octal number.

| Solution. The binary number given is  | 101 | 1110 | )   |

|---------------------------------------|-----|------|-----|

| Starting with LSB and grouping 3 bits | 001 | 011  | 110 |

| Octal equivalent                      | 1   | 3    | 6   |

Hence the octal equivalent number is  $(176)_8$ .

Since at the time of grouping the three digits in Example 1.14 starting from the LSB, we find that the third group cannot be completed, since only one 1 is left out in the third group, so we

complete the group by adding two 0s in the MSB side. This is called left padding of the number with 0. Now if the number has a fractional part then there will be two different classes of groups—one for the integer part starting from the left of the decimal point and proceeding toward the left and the second one starting from the right of the decimal point and proceeding toward the right. If, for the second class, any 1 is left out, we complete the group by adding two 0s on the right side. This is called right-padding.

**Example 1.15.** Convert 1101.0111<sub>2</sub> into an equivalent octal number.

| Solution. The binary number given is | 1101.0111        |  |

|--------------------------------------|------------------|--|

| Grouping 3 bits                      | 001 101. 011 100 |  |

| Octal equivalent:                    | 1 5 3 4          |  |

Hence the octal number is  $(15.34)_8$ .

Now if the octal number is given and you're asked to convert it into its binary equivalent, then each octal digit is converted into a 3-bit-equivalent binary number and—combining all those digits we get the final binary equivalent.

**Example 1.16.** Convert 235<sub>8</sub> into an equivalent binary number.

| Solution. The octal number given is | 235         |

|-------------------------------------|-------------|

| 3-bit binary equivalent             | 010 011 101 |

Hence the binary number is  $(010011101)_2$ .

Example 1.17. Convert 47.3218 into an equivalent binary number.Solution. The octal number given is4 7 3 2 13-bit binary equivalent100 111 011 010 001

Hence the binary number is  $(100111.011010001)_2$ .

#### 1.4.1.9 Conversion from a Binary to Hexadecimal Number and Vice Versa

We know that the maximum digit in a hexadecimal system is 15, which can be represented by 11112 in a binary system. Hence, starting from the LSB, we group four digits at a time and replace them with the hexadecimal equivalent of those groups and we get the final hexadecimal number.

**Example 1.18.** Convert 11010110<sub>2</sub> into an equivalent hexadecimal number.

| Solution. The binary number given is                     |      | 11010110 |  |

|----------------------------------------------------------|------|----------|--|

| Starting with LSB and grouping 4 bits                    | 1101 | 0110     |  |

| Hexadecimal equivalent                                   | D    | 6        |  |

| Hence the hexadecimal equivalent number is $(D6)_{16}$ . |      |          |  |

**Example 1.19.** Convert  $110011110_2$  into an equivalent hexadecimal number.

| Solution. The binary number given is                      |   | 110011110 |      |  |

|-----------------------------------------------------------|---|-----------|------|--|

| Starting with LSB and grouping 4 bits                     |   | 1001      | 1110 |  |

| Hexadecimal equivalent                                    | 1 | 9         | Е    |  |

| Hence the hexadecimal equivalent number is $(19E)_{16}$ . |   |           |      |  |

Since at the time of grouping of four digits starting from the LSB, in Example 1.19 we find that the third group cannot be completed, since only one 1 is left out, so we complete the group by adding three 0s to the MSB side. Now if the number has a fractional part, as in the case of octal numbers, then there will be two different classes of groups—one for the integer part starting from the left of the decimal point and proceeding toward the left and the second one starting from the right of the decimal point and proceeding toward the right. If, for the second class, any uncompleted group is left out, we complete the group by adding 0s on the right side.

**Example 1.20.** Convert 111011.011<sub>2</sub> into an equivalent hexadecimal number.

| Solution. The binary number given is                       |   | 111011.011 |        |  |

|------------------------------------------------------------|---|------------|--------|--|

| Grouping 4 bits                                            |   | 1011       | . 0110 |  |

| Hexadecimal equivalent                                     | 3 | В          | 6      |  |

| Hence the hexadecimal equivalent number is $(3B.6)_{16}$ . |   |            |        |  |

Now if the hexadecimal number is given and you're asked to convert it into its binary equivalent, then each hexadecimal digit is converted into a 4-bit-equivalent binary number and by combining all those digits we get the final binary equivalent.

**Example 1.21.** Convert 29C<sub>16</sub> into an equivalent binary number.

| Solution. The hexadecimal number given is                  | 2 9 C          |  |

|------------------------------------------------------------|----------------|--|

| 4-bit binary equivalent                                    | 0010 1001 1100 |  |

| Hence the equivalent binary number is $(001010011100)_2$ . |                |  |

**Example 1.22.** Convert 9E.AF2<sub>16</sub> into an equivalent binary number.

Solution. The hexadecimal number given is9 E.A F 24-bit binary equivalent1001 1110 1010 1111 0010Hence the equivalent binary number is (10011110.101011110010)2.

## 1.4.1.10 Conversion from an Octal to Hexadecimal Number and Vice Versa

Conversion from octal to hexadecimal and vice versa is sometimes required. To convert an octal number into a hexadecimal number the following steps are to be followed:

- i. First convert the octal number to its binary equivalent (as already discussed above).

- ii. Then form groups of 4 bits, starting from the LSB.

- iii. Then write the equivalent hexadecimal number for each group of 4 bits.

Similarly, for converting a hexadecimal number into an octal number the following steps are to be followed:

- i. First convert the hexadecimal number to its binary equivalent.

- ii. Then form groups of 3 bits, starting from the LSB.

- iii. Then write the equivalent octal number for each group of 3 bits.

**Example 1.23.** Convert the following hexadecimal numbers into equivalent octal numbers. (a) A72E (b) 4.BF85

#### Solution.

| ( <i>a</i> ) Given hexadecimal number is | A 7 2 E                                      |  |

|------------------------------------------|----------------------------------------------|--|

| Binary equivalent is                     | 1010 0111 0010 1110                          |  |

| =                                        | = 1010011100101110                           |  |

| Forming groups of 3 bits from the        | LSB 001 010 011 100 101 110                  |  |

| Octal equivalent 1 2 3 4 5 6             |                                              |  |

| Hence the octal equivalent of (A72       | 2E) <sub>16</sub> is (123456) <sub>8</sub> . |  |

| (b) Given hexadecimal number is    | 4 B F 8 5                                        |  |

|------------------------------------|--------------------------------------------------|--|

| Binary equivalent is               | 0100 1011 1111 1000 0101                         |  |

| =                                  | 0100.1011111110000101                            |  |

| Forming groups of 3 bits 100.10    | )1 111 111 000 010 100                           |  |

| Octal equivalent 4 5 7 7 0 2 4     |                                                  |  |

| Hence the octal equivalent of (4.E | BF85) <sub>16</sub> is (4.577024) <sub>8</sub> . |  |

**Example 1.24.** Convert (247)<sub>8</sub> into an equivalent hexadecimal number.

Solution. Given octal number is 2 4 7 Binary equivalent is 010 100 111 = 010100111Forming groups of 4 bits from the LSB 1010 0111 Hexadecimal equivalent A 7 Hence the hexadecimal equivalent of (247)<sub>8</sub> is (A7)<sub>16</sub>.

**Example 1.25.** Convert (36.532)<sub>8</sub> into an equivalent hexadecimal number.

Solution. Given octal number is 36532Binary equivalent is 011110101011010= 011110.101011010Forming groups of 4 bits 0001 1110. 1010 1101 Hexadecimal equivalent 1 E. A D Hence the hexadecimal equivalent of  $(36.532)_8$  is  $(1E.AD)_{16}$ .

# **1.5 Fixed Point Number Representation**

Fixed point numbers are a simple and easy way to express fractional numbers, using a fixed number of bits. Systems without floating-point hardware support frequently use fixed-point numbers to represent fractional numbers.

The Binary Point

The term "Fixed-Point" refers to the position of the binary point. The binary point is analogous to the decimal point of a base-ten number, but since this is binary rather than decimal, a different term is used. In binary, bits can be either 0 or 1 and there is no separate symbol to designate where the binary point lies. However, we imagine, or assume, that the binary point resides at a fixed location between designated bits in the number. For instance, in a 32-bit number, we can assume that the binary point exists directly between bits 15 (15 because the first bit is numbered 0, not 1) and 16, giving 16 bits for the whole number field is generally designated as the sign bit leaving 15 bits for the whole number's magnitude.

#### Width and Precision

The width of a fixed-point number is the total number of bits assigned for storage for the fixedpoint number. If we are storing the whole part and the fractional part in different storage locations, the width would be the total amount of storage for the number. The **range** of a fixedpoint number is the difference between the minimum number possible, and the maximum number possible. The precision of a fixed-point number is the total number of bits for the fractional part of the number. Because we can define where we want the fixed binary point to be located, the precision can be any number up to and including the width of the number. Note however, that the more precision we have, the less total range we have.

There are a number of standards, but in this book we will use  $\mathbf{n}$  for the width of a fixed-point number,  $\mathbf{p}$  for the precision, and  $\mathbf{R}$  for the total range.

Examples

Not all numbers can be represented exactly by a fixed-point number, and so the closest approximation is used.

The formula for calculating the integer representation (X) in a Qm.n format of a float number (x) is:

$X = round(x*2^n)$

To convert it back the following formula is used:

$x = X * 2^{-n}$

Some examples in Q3.4 format:

| After conversion:                 | After converting them back: |

|-----------------------------------|-----------------------------|

| 0100.0110 = 4 + 3/8               | 4 + 3/8                     |

| 0001.0000 = 1                     | 1                           |

| 0000.1000 = 1/2                   | 1/2                         |

| 0000.0101 = 5/16                  | 0.3125                      |

| 0000.0100 = 1/4                   | 1/4                         |

| 0000.0010 = 1/8                   | 1/8                         |

| 0000.0001 = 1/16                  | 1/16                        |

| 0000.0000 = 0                     | 0                           |

| 1111.1111 = -1/16                 | -1/16                       |

| 1111.0000 = -1                    | -1                          |

| 1100.0110 = -4 + 3/8 = -(3 + 5/8) | -4 + 3/8                    |

|                                   |                             |

Randomly chosen floats:

| 0000.1011 = 0.673 $0.6875$ |  |

|----------------------------|--|

| 0000.1011 - 0.075 0.0875   |  |

| 0110.0100 = 6.234 6.25     |  |

Some examples in the (extremely common) Q7.8 format:

$0000_0001.0000_0000 = +1$ 1000\_0001.0000\_0000 = -127

#### 0000 0000.0100 0000 = 1/4

#### Arithmetic

Because the position of the binary point is entirely conceptual, the logic for adding and subtracting fixed-point numbers is identical to the logic required for adding and subtracting integers. Thus, when adding one half plus one half in Q3.4 format, we would expect to see:

0000.1000 +0000.1000

=0001.0000

Which is equal to one as we would expect. This applies equally to subtraction. In other words, when we add or subtract fixed-point numbers, the binary point in the sum (or difference) will be located in exactly the same place as in the two numbers upon which we are operating.

When multiplying two 8-bit fixed-point numbers we will need 16 bits to hold the product. Clearly, since there are a different number of bits in the result as compared to the inputs, the binary point should be expected to move. However, it works exactly the same way in binary as it does in decimal.

When we multiply two numbers in decimal, the location of the decimal point is N digits to the left of the product's rightmost digit, where N is sum of the number of digits located to the right side of the decimal point in the multiplier and the multiplicand. Thus, in decimal when we multiply 0.2 times 0.02, we get:

0.2 x0.02

0.004

The multiplier has one digit to the right of the decimal point, and the multiplicand has two digits to the right of the decimal point. Thus, the product has three digits to the right of the decimal point (which is to say, the decimal point is located three digits to the left).

It works the same in binary.

From the addition example above, we know that the number one half in Q3.4 format is equal to 0x8 in hexadecimal. Since 0x8 times 0x8 in hex is 0x0040 (also in hex), the fixed-point result can also be expected to be 0x0040 - as long as we know where the binary point is located. Let's write the product out in binary:

#### 000000001000000

Since both the multiplier and multiplicand have four bits to the right of the binary point, the location of the binary point in the product is eight bits to the left. Thus, our answer is 00000000.01000000, which is, as we would expect, equal to one quarter.

If we want the format of the output to be the same as the format of the input, we must restrict the range of the inputs to prevent overflow. To convert from Q7.8 back to Q3.4 is a simple matter of shifting the product right by 4 bits.

sine table

Many embedded systems that produce sine waves, such as DTMF generators, store a "sine table" in program memory. (It's used for approximating the mathematical sine() and cosine() functions). Since such systems often have very limited amounts of program memory, often fixed-point numbers are used two different ways when such tables are used: the values stored in the tables, and the "brads" used to index into these tables.

#### values stored in sine table

Typically one quadrant of the sine and cosine functions are stored in that table. Typically it is a quadrant where those functions produce output values in the range of 0 to +1. The values in such tables are usually stored as fixed point numbers -- often 16-bit numbers in unsigned Q0.16 format or 8-bit numbers in unsigned Q0.8 values. There seems to be two popular ways to handle the fact that Q0.16 can't exactly handle 1.0, it only handles numbers from 0 to  $(1.0-2^{-16})$ : (a) Scale by exactly a power of two (in this case 2^16), like most other fixed-point systems, and replace (clip) values too large to store as that largest value that can be stored: so 0 is represented as 0, 0.5 represented as 0x8000,  $(1.0-2^{-16})$  represented as 0xFFFF, and 1.0 truncated and also represented as 0xFFFF. (b) Scale by the largest possible value (in this case 0xFFFF), so both the maximum and minimum values can be represented exactly: so 0 is represented as 0,  $(1.0-2^{-16})$  represented as 0xFFFF.

A few people draw fairly accurate circles and calculate fairly accurate sine and cosine with a Bezier spline. The "table" becomes 8 values representing a single Bezier curve approximating 1/8 of a circle to an accuracy of about 4 parts per million, or 1/4 of a circle to an accuracy of about 1 part in a thousand.

turns

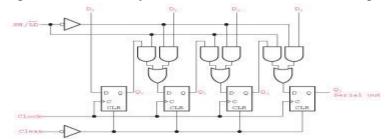

Many people prefer to represent rotation (such as angles) in terms of "turns". The integer part of the "turns" tells how many whole revolutions have happened. The fractional part of the "turns", when multiplied by 360 (or  $1\tau = 2\pi$ ) using standard signed fixed-point arithmetic, gives a valid angle in the range of -180 degrees ( $-\pi$  radians) to +180 degrees ( $+\pi$  radians). In some cases, it is convenient to use unsigned multiplication (rather than signed multiplication) on a binary angle, which gives the correct angle in the range of 0 to +360 degrees ( $+2\pi$  radians).